Teaching Activities at University of Potsdam:

- Chip Design (6 ECTS)

- Processor Design for AI Applications: From System to Transistor (6 ECTS, BSc and MSc)

- Hardware Architectures for AI Applications (6 ECTS, BSc and MSc)

- Hardware Defects, Faults, Errors, and Failures: Yield, Reliability, and Dependability (6 ECTS, BSc and MSc)

- Seminar on Neuromorphic Chip Design (3 ECTS, BSc and MSc)

- System on Chip Architectures (6 ECTS, BSc and MSc)

- Computer Vision Hardware Architecture (3 ECTS, BSc and MSc)

- Seminar: Ethics for Nerds (3 ECTS, BSc and MSc)

Teaching Activities at Technical University of Munich:

- Practical Course: Accelerating Convolutional Neural Networks using Programmable Logic (10 ECTS, BSc and MSc) (Prof. Schulz)

- Seminar Course: Development and Integration of Hardware Accelerators (5 ECTS, BSc and MSc) (Prof. Schulz)

- Seminar: Ethics for Nerds (6 ECTS, BSc and MSc) (Prof. Trinitis)

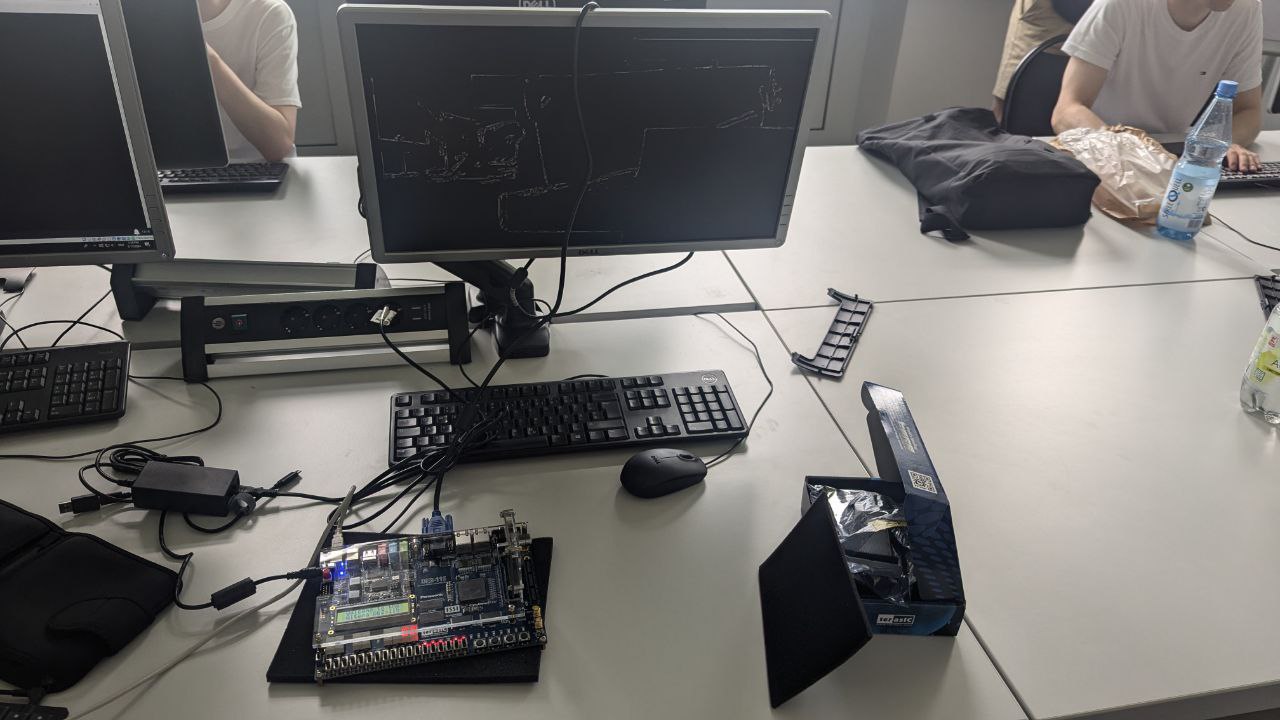

- Practical Course: Introduction to Hardware Design Languages and Tools (6 ECTS, BSc) (Prof. Trinitis)

- Selected Topics in Big Geospatial Data (5 ECTS, BSc and MSc)

- Lab Course Mobile Computer Vision (5 ECTS, BSc)

- Lab Course Photogrammetric Data Acquisition (5 ECTS, BSc)

- Engineering Projects (6 ECTS, BSc)

Joint Curriculum "Edge AI":

| Course Title | ECTS | Course Hours | Performance Evaluation |

|---|---|---|---|

| Chip Design | 6 | 4 hours/week | Project and oral exam |

| Processor Design for AI Applications: From System to Transistor | 6 | 4 hours/week | Oral exam |

| Hardware Architectures for AI Applications | 6 | 4 hours/week | Oral exam |

| Seminar on Neuromorphic Chip Design | 3 | 2 hours/week | Presentation and report |

| System on Chip Architectures | 6 | 4 hours/week | Project and presentation |

| Computer Vision Hardware Architecture | 3 | 2 hours/week | Presentation and report |

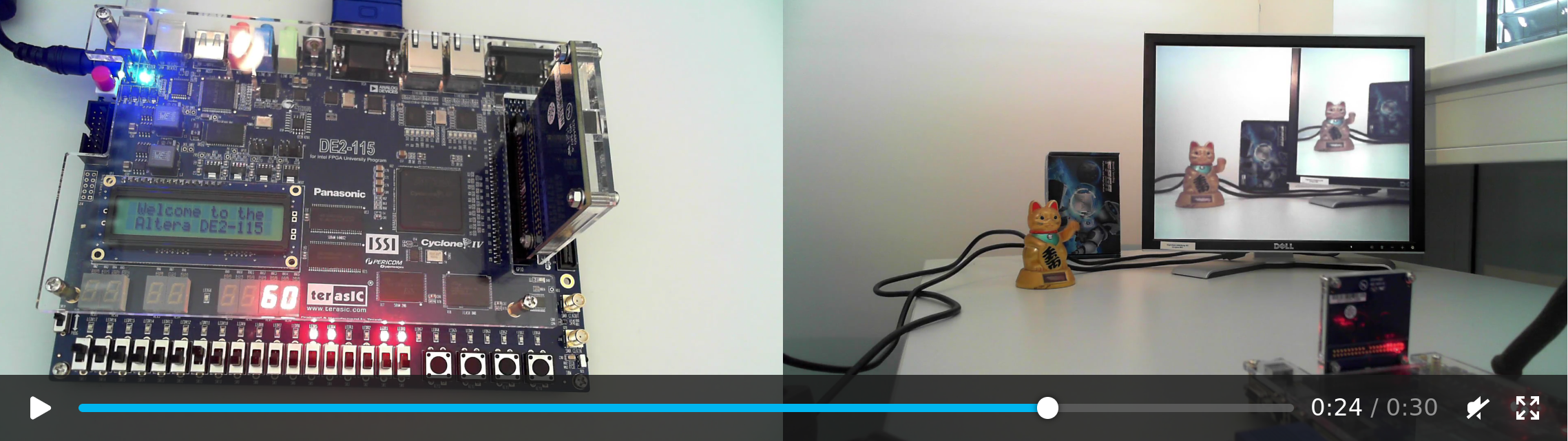

| Practical Course: Accelerating Convolutional Neural Networks using Programmable Logic | 10 | Project, presentation and report | |

| Seminar Course: Development and Integration of Hardware Accelerators | 5 | Presentation and report |

Highlights: